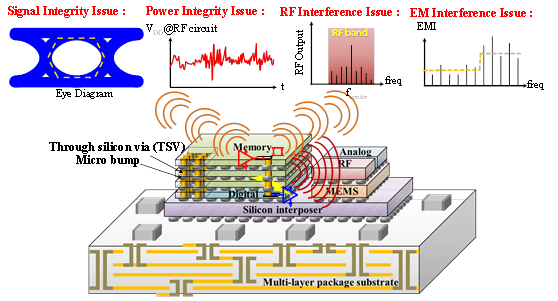

Due to the physical constrain, the miniaturization technique of the transistors manufacture is approaching its limit. To keep Moore’s law, three-dimensional integrated circuit (3-D IC) technology has been considered as the main approach to exceed Moore’s law or more than Moore. 3-D IC is fabricated using several chips stacked vertically and interconnected by through silicon vias (TSVs). Besides the smaller form factor, 3-D IC technology can provides other advantages including the higher speed transmission rate, lower power consumption, and the feasibility of heterogeneous integration. In the 3-D IC, reducing the electromagnetic noise inference either in intra-system or inter-system plays an important role. Our researches focus on how to control, evaluate and measure the level of the noise interference, including the construction of the electromagnetic simulation environment, solutions for the suppression of noise coupling, and the noise measurement platform.